电子电气工程师技术丛书

点击查看第二章

点击查看第三章

PDN设计之电源完整性:高速数字产品的鲁棒和高效设计

Principles of Power Integrity for PDN Design:

Robust and Cost Effective Design

for High Speed Digital Products

[美]拉里·D.史密斯(Larry D. Smith)

埃里克·博加廷(Eric Bogatin)著

陈会 张玉兴译

第1章

电源分配网络工程

1.1 电源分配网络的定义及关心它的原因

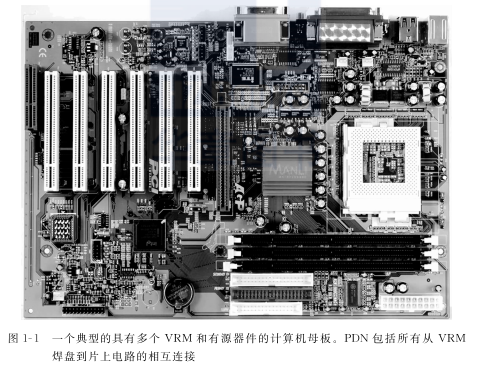

电源分配网络(PDN)包括从电压调整模块(VRM)到片上电路的所有电源间的相互连接。一般而言,它包括印制板上电源和地平面、电缆、连接器和所有与电源有关的电容器。图1-1是一个典型的计算机印制板的例子,它具有多个VRM和传递电源、地到所有有源器件焊盘的路径。

PDN的目的如下所示。

- 为实现所有功能的有源器件分配低噪声DC电压和电源。

- 对所有信号提供低噪声回路。

- 为减轻电磁干扰(EMI)问题,不贡献辐射。

本书聚焦于PDN的第一个作用:对所有需要电源的有源器件分配DC电压和电源,保证噪声低于可接受的水平。PDN中不成功的噪声控制会促使信号眼图缩小。由于电压噪声的存在,眼图在垂直方向上的幅度会发生重叠。信号与参考点相交的时间在水平方向上扩展,产生抖动并且减小眼图的张开程度。内部核心电路可能会被设置并且引起保持时间错误,从而导致功能失效。

提示

不能正确设计PDN的后果是增加了位错误率,这来自在I/O电路和芯片内部电路中提高的垂直噪声和抖动。核心电路中过度的水平噪声可导致重新设置和持时间错误。

依赖于开关门电路,PDN噪声会附加到来自发射机(TX)的信号上。在接收机(RX)中,它也能以电压参考噪声的形式出现。这两种情况都会降低其他源可用的噪声裕度。

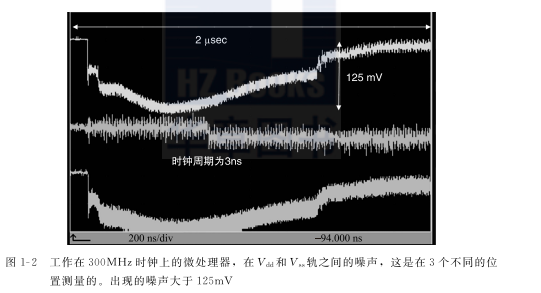

图1-2所示为在微处理器的三个不同片上位置和两个不同的电压轨上,测量核心电源和地之间的电压噪声。这个例子中的电压噪声是125mV。在大部分电路中,这种电压噪声的大部分会叠加在RX信号上。

即使这个噪声本身不足以引起位失效,但是它会促使眼图闭合,加上其他的噪声源可能会导致位失效。

芯片电源轨上的电压噪声也影响定时。传输延时是输入电压的跃变通过序列门传送给输出电压后发生跃变的时间,依赖于瞬时电压的电平。漏—源电压越高,沟道的电场越强,延迟时间越短。同样,Vdd与Vss之间的电压越低,传输延时越长。

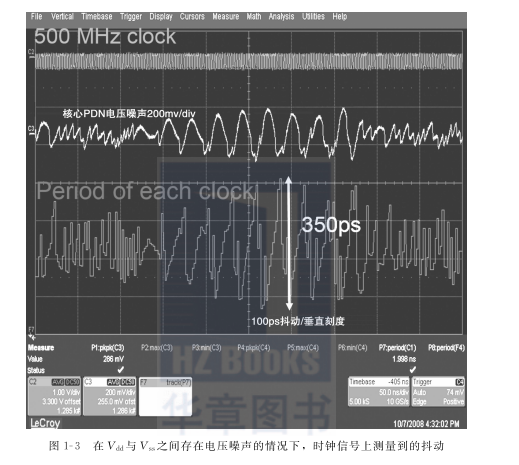

这意味着:片上Vdd与Vss之间的电压噪声对输出信号的定时变化有着直接的贡献,这被称为“抖动”。较高的Vdd轨电压吸引在时钟边缘内,而较低的轨电压则推出时钟边缘。图1-3所示为测量感应在高端FPGA测试芯片上的抖动,其中电压噪声来自PDN。

这个例子中,时钟分配网络与其他很多门共同使用Vdd。这些门用伪随机位序列(PRBS)来开启,从PDN中抽取大的电流,产生大的瞬时电压噪声。电压噪声加到时钟分配网络的门上,引起时钟信号定时的变化。其周期是从一个时钟边缘到下一个时钟的边缘,测量这个抖动周期可以证明片上的电压噪声和时钟抖动直接相关。

在这个例子中,PDN噪声引起抖动的灵敏度是1mV的噪声引起1ps时间内的抖动。100mV的峰峰PDN噪声大概贡献100ps的峰峰抖动。在一个2GHz的时钟系统中,其周期仅为500ps。PDN噪声单独引起的抖动就会花费整个定时“预算”。

提示

在这个例子中,PDN噪声抖动灵敏度大约是1ps/mV,这足以估算出很多器件中的灵敏度。

1.2 PDN工程

为满足电压噪声和定时“预算”的要求,PDN上的电压噪声必须低于一些特定值。这与系统的详细组成有关,电压噪声的限制大约是供电电压的±5%。在以单极性信号的CMOS为基础的数字系统中,接收机总的噪声裕度大约是信号摆动的15%。除非有不可抗拒的理由,一般我们为3个占支配地位的噪声源(反射噪声、交调和PDN噪声)等分这个“预算”,这就是PDN的典型噪声指标为5%的来源。

在一些如模数转换(ADC)或锁相环(PLL)应用中,它们的性能对电压噪声非常敏感,PDN噪声必须低于1%。从直流到高达5~10GHz的信号带宽,PDN噪声一直要保持在限制以下。

与其他的信号完整性问题一样,排除它们的第一步是要找到根源。在低频,由于附着在PDN上的电压噪声一般来源于VRM的电压噪声,所以设计的第一步是在适当负载电流下选择具有足够低电压噪声的VRM。

即使是世界上最稳定的VRM,电压噪声仍旧存在于芯片的焊盘上,这是由通过芯片门的瞬时电源电流在整个PDN上的阻抗压降引起的。在VRM的焊盘与片上焊盘之间是与PDN关联的相互连接线。我们称这整个网络为PDN生态学。

提示

PDN生态学是指一系列从芯片焊盘到VRM焊盘的相互连接。它们之间相互影响以产生应用在芯片上的阻抗曲线并感应出了PDN噪声。

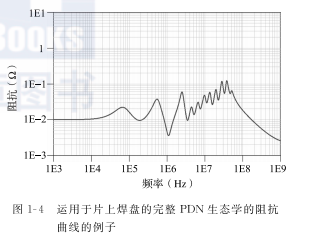

应用于片上焊盘的这些相互连接对阻抗曲线有所贡献,图1-4所示为典型的例子。

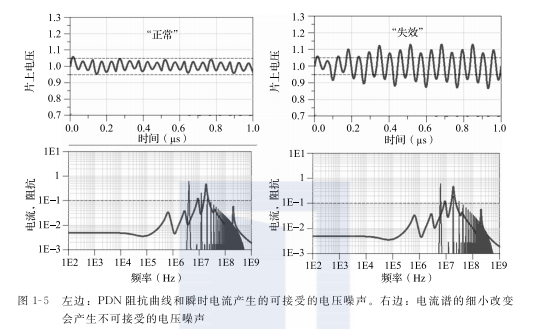

任何瞬时电流通过阻抗曲线都会在芯片的焊盘上产生与VRM稳定性相关联的电压噪声,例如,图1-5所示为当执行特殊微码时,在器件的核心电源轨上绘出的瞬时电流谱。与电流谱成一列的是该电流流过的阻抗曲线。在每一个频率下电流幅度和阻抗的结合产生了电压噪声谱。当在时域观察时,这些噪声谱就是瞬时电压噪声。

图1-5左边所示为瞬时电流谱、PDN阻抗曲线和由此在电源轨上产生的电压噪声。电流谱的峰值与阻抗峰值组合产生可接受的噪声。图1-5右边是同样的阻抗曲线,但是它具有不同的微码算法,以稍微不同的频率驱动同样的门。电流谱峰值的结尾与大的阻抗峰值相重叠,产生的电源电压噪声超出了可接受的范围。

实际的电压噪声由瞬时电流通过阻抗曲线产生,它依赖于电流频率分量和阻抗曲线峰的重叠。如果电压噪声低于特定值,则PDN感应的误差不会发生。如果微码改变引起电流振幅峰和频率分量的变化,则它们与阻抗峰重叠就会产生更大的电压噪声,并引起产品失效。

提示

PDN上的噪声在很大程度依赖于加到片上的阻抗曲线和通过芯片的瞬时电流谱。微码的细节和门的应用对PDN噪声的产生有很大的影响。

1.3 PDN的鲁棒性设计

驱动芯片上门的特殊微码会引起性能的多样性,这使测试产品的PDN设计变得很困难。如果电流谱峰和阻抗峰的组合产生小于规定的瞬时噪声,那么一个产品在启动时或者当工作在特别的软件测试套件时可能工作得很好。产品设计通过这个测试,并且被认为是“可工作”的。

可是,如果工作在另外的软件套件下,并驱动更多的门开关工作在不同的主环路频率下,同时巧合的是峰值PDN阻抗曲线发生重叠,那么较大的瞬时压降发生,相同的产品会失效。

虽然产品在开始时运行了测试软件套且呈现的工作是令人鼓舞的,但这并不能保证它的鲁棒性。当产品被大范围的用户软件驱动时,被评估的“可工作”产品常常有现场故障。

鲁棒性PDN设计意味着在任何软件下都可工作,在具有任何时域特征的任意频率下都可产生最大瞬时电流。在此电流下,通过阻抗曲线产生的最差电压总小于引起失效的电压。

最差情况下的瞬时电流和电压噪声指标一起设置了最大可允许电压噪声的限制,PDN阻抗等电压噪声是不能超过这个限制的。

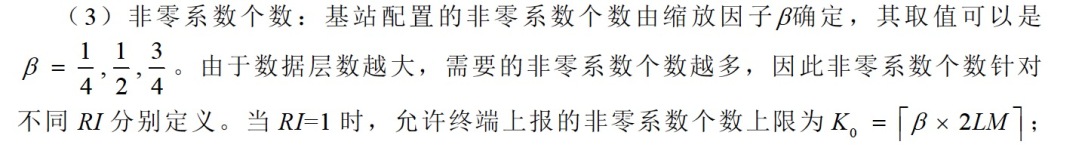

这个最大的可允许且可保证性能的PDN阻抗称为PDN设计中的目标阻抗,我们由文献[1]可推导得:

式中,Ztarget是任意频率下的可允许阻抗;ΔVnoise是满足性能要求时规定的最大电压轨噪声;Imax-transient是在任何可能的工作条件下最差情况的瞬时电流。

例如,如果噪声指标为±50mV,最差情况下的瞬时电流是1A,则目标阻抗为

如果ΔVnoise或者Imax-transient是频率的函数,那么Ztarget也是频率的函数。

原理上,整个电流谱分布和整个阻抗曲线的组合就是产生最差峰值电压噪声的根源。不幸的是,这仅能用包含详细瞬时电流波形和完整PDN阻抗曲线的瞬态仿真才能确定。实际上,作为优值的目标阻抗是很有用的近似,它使我们在PDN设计中有一个好的开端。

提示对PDN而言,目标阻抗是很有用的优值。在PDN鲁棒性设计中,它是设计目标的很好的近似。鲁棒性PDN设计的最终评估将来自整个PDN和瞬时电流波形的瞬态仿真。

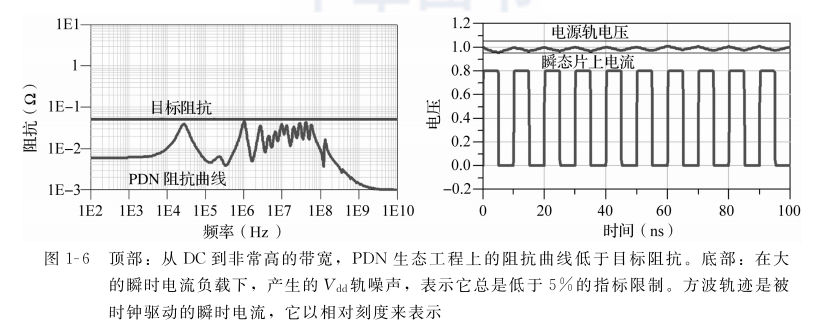

充分的鲁棒性PDN是由目标阻抗来定义的。如果加到片上焊盘的完整PDN生态学的阻抗,在所有频率下都低于目标阻抗,那么瞬时电流流过这个PDN阻抗产生的最差的电源轨噪声将不会超过噪声指标,除非是在非常罕见的恶劣波形场合。图1-6所示为在所有的频率下阻抗曲线低于50mΩ目标阻抗的例子,这也是具有大电流负载的轨电压噪声的例子。

提示在评估PDN性能时,目标阻抗是最重要的度量。PDN阻抗越高于目标阻抗,失败的风险越大。

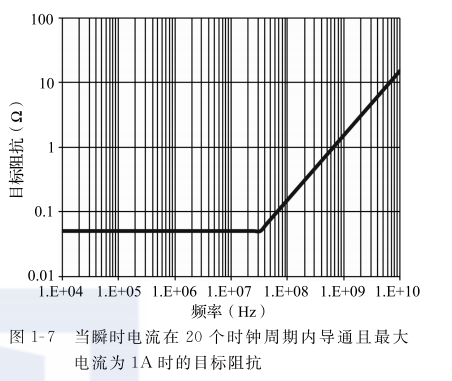

实际上,通过片上的最大最差瞬时电流在所有频率下都不是平坦的。在高频端,这个最大电流的幅度一般会下跌,它与开关门导通的速度有关。详细情况与芯片构成、传递的位数和微码的性质有关。有效的上升时间是从时钟边沿的上升时间到100个时钟周期的时间。

例如,如果时钟频率是2GHz、周期是0.5ns、建立开关门最多需要20个周期,那么最差的瞬时电流导通的最短上升时间是0.5ns×20个周期=10ns。最大瞬时电流频率分量的幅度超过0.35/10ns=35MHz后开始滚降。超过35MHz后,最差瞬时电流谱以-20dB/十倍频程的速度滚降,由此得到的目标阻抗将随着频率而增加。在这个例子中目标阻抗如图1-7所示,假设轨电压噪声指标为50mV、最差电流为1A。

这种行为的后果是在高频时目标阻抗指标被放宽。预测频率的膝点常常是困难的,除非知道瞬时电流和最差微码的详情。

实际上这个分析指出:准确地计算瞬时电流和PDN目标阻抗的精确要求是非常困难的。人们总是应用工程判断把可用信息转换成高性价比设计。

设计PDN的过程如下所示:

- 基于已知芯片的功能和应用,建立目标阻抗的最好猜想。

- 为满足可能的阻抗曲线,做出工程决定。

- 在PDN阻抗实现价格与目标阻抗和现场失败风险之间达到平衡折中。

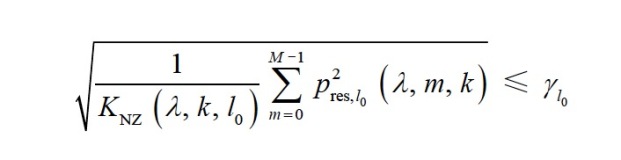

工作在额定性能的电路失败风险的粗略测度是实际的PDN阻抗与目标阻抗之比,术语为PDN比:

比值小于1表示PDN失效风险低,随着这个值的增加,风险也增加。从实际经验来看,比值2仍旧是可接受的风险,但是比值达10的结果则说明这个风险是不可接受的。虽然很多微码工作在额定性能下,但一些可能激励PDN谐振,并使产品发生稳定性问题。

一般而言,若实现低阻抗PDN,则具有较低的风险比,价格更高,其原因是如下之一:需要更多的元件,紧凑的装配设计影响产值,需要多层印制板或者多层封装,容量增加了面积或者使用了更加昂贵的材料。价格和风险之间的平衡常常成为一个问题,——你能承受多大的风险。为增加裕度,你要付出会更多,你总是要“买保险”以减小风险。这就是PDN设计中的基本折中。

提示

PDN设计中重要的风险测度是PDN比,它是峰值阻抗与目标阻抗之比。PDN比小于等于2是低风险,而PDN比大于等于10则是高风险。

在消费品应用中,常常存在强有力的价格驱动,工程上低价格设计的高风险比可能是较好的平衡。可是,例如在航空电子系统中,为了使风险比小于1,付出额外的费用才是高性价比的解。在价格和风险之间,不同的应用有不同的平衡。

1.4 建立PDN阻抗曲线

PDN的设计目标是从DC到任何电源电流的最高频率分量中,都设计可接受的阻抗曲线。所有的PDN元件应该一起设计,以实现整个系统的阻抗曲线。虽然很多元件相互影响,但在PDN设计中规定特性的阻抗曲线里指定一些特性作用,这是可能的。

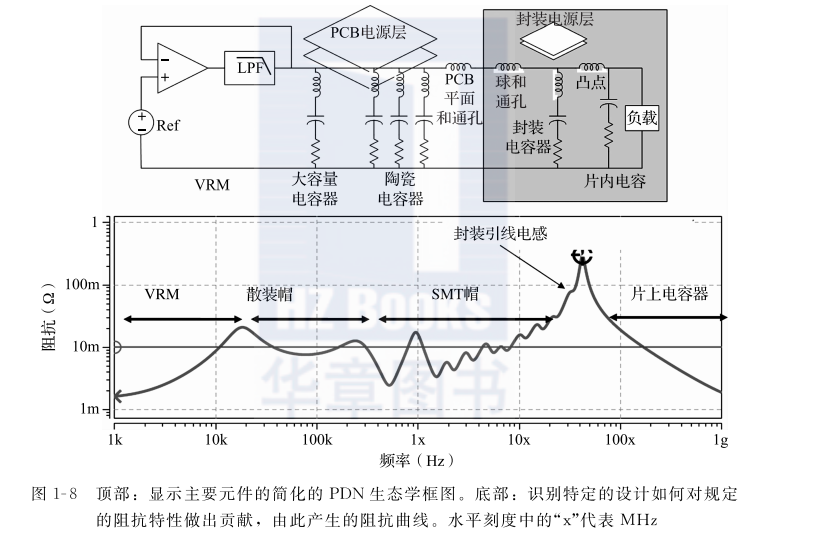

图1-8所示为完整PDN生态学的简化框图。它包含片上电容、可能的封装电容、封装引线电感、电路板通孔、电路板上的电源和地平面、去耦电容器、大容量电容器和VRM。

可单独作用的一些PDN元件使我们能优化PDN其他独立部分,只要关注一个元件的阻抗与相互作用的另外元件的阻抗的接口就可。这就是为什么多数PDN设计与部件之间相互作用的接口有关。

在未来的历程中,我们探索构成PDN的元件中的每一个,了解它们的相互作用是如何影响鲁棒性和高性价比的PDN设计的。最终,电源完整性工程是负责任地找到价格、风险、性能和研发周期之间可接受的平衡点。我们知道PDN元件的详情越多,就能越快地找到可接受的解。

1.5 总结

1.PDN是由从片上焊盘到VRM之间的所有相互连接和它们之间的所有元件组成的。

2.PDN的目的是为器件提供干净、低噪声电压,为器件提供地电源,为信号提供低阻抗回路并减轻EMC问题。

3.PDN中容差的典型噪声指标是5%,这是基于主要噪声源1/3噪声“预算”的分配额的,主要的噪声源是反射噪声、交调和PDN。

4.PDN上的电压噪声是瞬时电源电流通过PDN阻抗的结果。噪声是阻抗曲线和瞬时电流谱组合的结果。

5.PDN噪声贡献于抖动,典型的灵敏度是1ps/mV的噪声。这个数值随芯片设计和器件的技术节点而变。

6.应用于片上焊盘的阻抗曲线是PDN质量和性能最重要的度量,其范围为DC到开关信号的最高频率分量。

7.目标阻抗是最大阻抗的测度,其最差的电压噪声应该低于可接受的指标。

8.PDN比是实际的PDN峰值阻抗与目标阻抗之比,它是风险的度量。若PDN比大于10则是高风险设计。

9.刻画阻抗曲线需要优化PDN的单独元件和它们之间的相互作用,整个PDN系统必须为减小峰值而优化。

10.如果你关心PDN设计,那么本书正好适合你。

参考文献