**项目背景

**

目前互联网上的图片还是以JPEG格式为主,伴随新的图像视频编解码技术的发展,也产生了多种更高效的图片编解码算法,这些高效的图片编解码算法相比JPEG图片格式可以提升50%以上的压缩率。如果客户端对图片的请求采用高压缩率图片格式,可以相应减少50%以上的传输带宽,可以有效提升用户的图片下载体验。

但是,随着算法压缩率的提升,编码算法的计算复杂度也越来越高,采用通用CPU进行编码成本很高,导致很难在业务中全面推广。

因此,硬件FPGA编解码方案替代通用CPU方案,通过提高计算效率和计算密度,来降低硬件成本很有实际意义。

开发实施

整个项目分为编码功能验证和编码性能提升两个阶段进行开发:

编码功能验证阶段使得FPGA运行在100Mhz主频,主要用来分析编码效果和图片质量。

编码性能提升阶段将主频提升到300Mhz,同时实现多个IP并行编码,目标:相比CPU服务器实现性能提升25倍。

技术层次结构

整个项目开发涉及FPGA逻辑开发、软件开发。

FPGA在服务器中作为通用CPU的协处理器,以PCIE卡的形式与通用CPU连接。

FPGA处理系统基于AliFPGA逻辑平台开发。

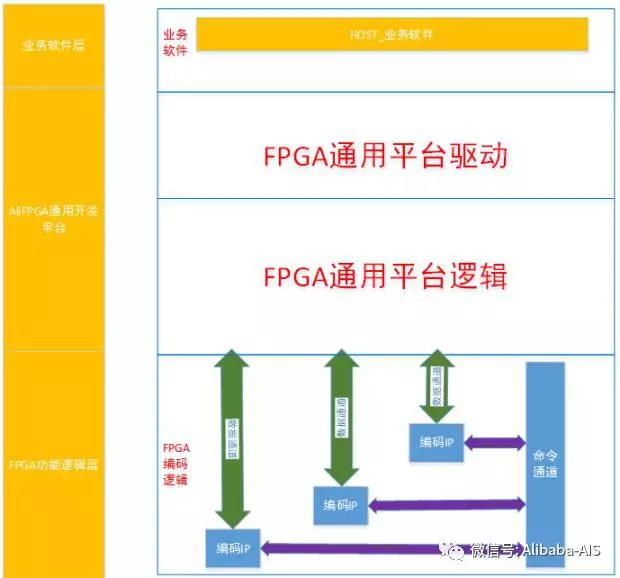

项目整体的层次结构如下:

图1 系统层次结构图

整体层次结构可以分为FPGA功能逻辑层、AliFPGA通用开发平台、业务软件层三个层次:

- FPGA功能逻辑层*

主要实现高压缩率图片格式编码功能。

AliFPGA通用开发平台

该层为标准的AliFPGA通用开发平台,主要实现软件与FPGA功能逻辑的交互,分为FPGA部分和驱动部分。驱动部分负责给业务软件部分提供访问的命令接口及数据接口。

- 业务软件层*

该层实现网络通信及业务逻辑等。

关键优化点

FPGA高性能数据处理需要综合考虑系统流水线设计、FPGA逻辑主频提升、软件设计等多个方面:

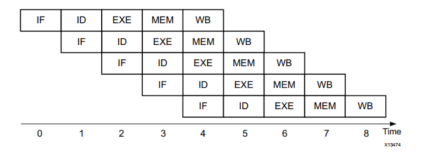

FPGA硬件编码流水线优化

流水线定制是FPGA较之通用CPU的优势所在。在FPGA中,每个功能模块硬件资源独立,无需竞争。通过合理设计流水线的划分,可以优化流水线吞吐量。

我们对标准编码流程进行了解耦合,进行了流水拆分。将整个图片编码流水线由2级流水,优化到4级流水。

解耦后的流水方案吞吐量是标准编码流程的2倍。

- 基于FPGA逻辑主频提升*

对于FPGA高性能计算,除了采用流水线、乒乓等技术外,提升每个功能逻辑IP的运行频率,是性能优化非常关键的一步。

项目中通用逻辑平台运行在250Mhz和300Mhz时钟;功能逻辑IP运行在用户时钟域300MHz。

对于功能逻辑IP时钟域,我们通过识别硬件算法的关键路径,并对其进行针对性优化,通过降低无关逻辑的耦合性以及优化寄存器扇出等方法综合起来将图像编码核的频率提升3倍。

- 软件设计*

软件层的主要功能是把来自调度层的图片原始文件下发给FPGA编码核,同时将编码后文件返回给软件调度层。

软件设计中重点考虑以下几点:

1) 应用层的多并发支持

2) 驱动层的多IP支持

3) 多通道之间的负载均衡

性能提升

本项目基于FPGA芯片实现了高压缩率图片编码加速: 运行频率300Mhz,结合功能逻辑IP多通道并发,在实际评测中相比当前高性能通用CPU服务器(64核),整体性能提升了25倍。

小结

从我们的性能评测中可以看出基于FPGA编解码方案在性能上优于传统CPU方案,未来可以考虑更多采用FPGA方案提供服务,释放更多CPU资源用于其他服务。