1. 概述

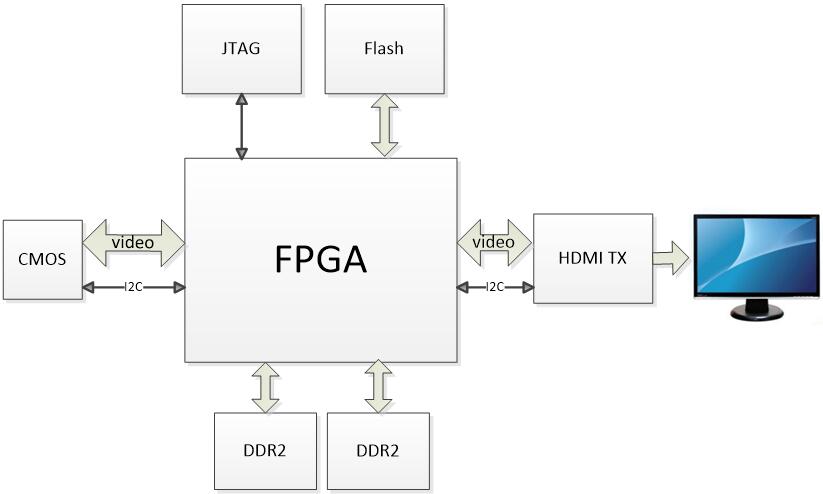

本设计采用FPGA技术,将CMOS摄像头(MIPI接口)的视频数据经过采集、存储、帧率转换及格式转换,最终通过HDMI接口显示在电视屏幕上。

2. 硬件系统框图

CMOS采用300万像素的摄像头芯片,其他部分可参考博文“FPGA设计——CMOS摄像与HDMI显示(DVP版)”。

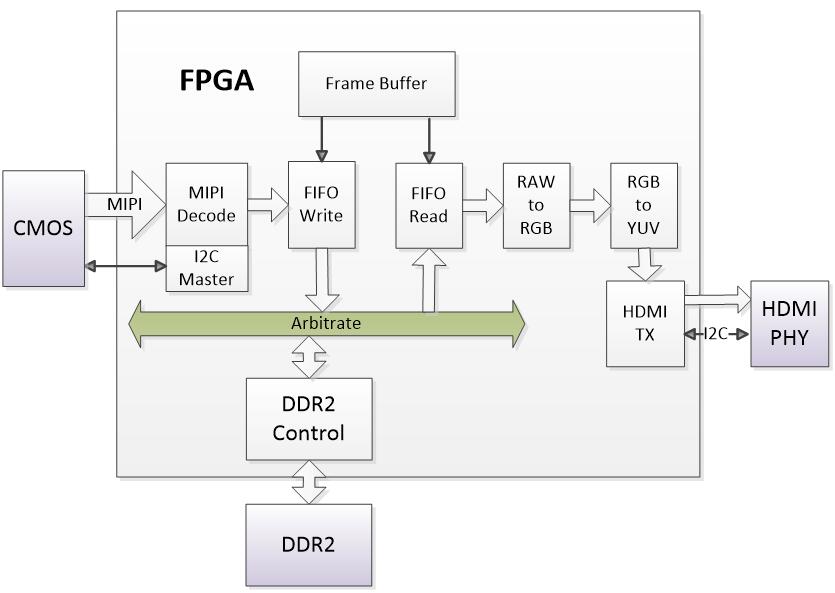

3. FPGA逻辑框图

FPGA各部分逻辑模块如下图所示:

-

MIPI DECODE,解析MIPI串口数据;

-

I2C Master,配置CMOS芯片;

-

DDR2 Control,配置与控制DDR2芯片组,实现读写仲裁;

-

FIFO Write,将采集到的视频数据跨时钟域地写进DDR2中;

-

FIFO Read,将DDR2中的数据跨时钟域地读出给后续图像处理模块;

-

Frame Buffer,负责FIFO Write和FIFO Read的调度,实现帧率转换;

-

RAW to RGB,将原始RAW8数据转换成RGB888数据;

-

RGB to YUV,将RGB888数据转换成YUV422数据;

-

HDMI TX,将处理好的视频数据发送给HDMI PHY芯片,同时通过I2C接口配置HDMI PHY芯片。

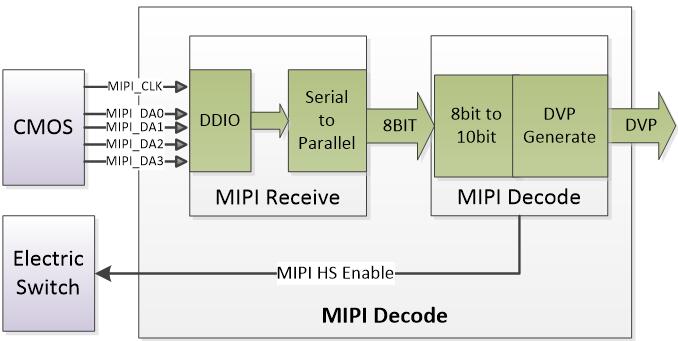

4. MIPI解码模块

这里以4-lan 10bit模式为例,介绍MIPI解码模块设计。

-

DDIO,负责将DDR模式的时钟和数据转换成单边沿的数据与时钟(上升沿);

-

Serial to Parallel,将串行数据转换成并行数据(8比特);

-

8bit to 10bit,负责解析出10bit模式的4通道数据;

-

DVP Generate,生成DVP格式的视频流。

下面再介绍一下8bit到10bit的原理,关于更多的MIPI原理可参考博文"海思Hi3516A(2)MIPI":

在数据传输时,以通道1->通道2->通道3->通道4->通道1...为循环传输8bit数据,每5个8比特数据组成4个10比特数据,第1->第4个8比特数据为4个10比特数据的高8位,第5个8比特数据为4个10比特数据的低2位的从高到低的拼接。

5. CMOS配置

将摄像头芯片配置成2048*1536分辨率25帧的视频输出,参考寄存器配置如下:

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

|

module i2c_cfg_par(

input clk,

input [07:0] lut_index,

output reg [23:0] lut_data

);

always @(*)

begin

case

(lut_index)

//sc3035 setting

'd0 : lut_data <= '

h0103_01;

// soft reset

'd1 : lut_data <= '

h0100_00;

'd2 : lut_data <= '

h4500_31;

// rnc sel

'd3 : lut_data <= '

h3416_11;

'd4 : lut_data <= '

h4501_a4;

// bit ctrl

'd5 : lut_data <= '

h3e03_03;

// aec

'd6 : lut_data <= '

h3e08_00;

'd7 : lut_data <= '

h3e09_1f;

'd8 : lut_data <= '

h3e01_30;

'd9 : lut_data <= '

h322e_00;

'd10 : lut_data <= '

h322f_af;

'd11 : lut_data <= '

h3306_20;

'd12 : lut_data <= '

h3307_17;

'd13 : lut_data <= '

h330b_54;

'd14 : lut_data <= '

h3303_20;

'd15 : lut_data <= '

h3309_20;

'd16 : lut_data <= '

h3308_08;

'd17 : lut_data <= '

h331e_16;

'd18 : lut_data <= '

h331f_16;

'd19 : lut_data <= '

h3320_18;

'd20 : lut_data <= '

h3321_18;

'd21 : lut_data <= '

h3322_18;

'd22 : lut_data <= '

h3323_18;

'd23 : lut_data <= '

h330c_0b;

'd24 : lut_data <= '

h330f_07;

'd25 : lut_data <= '

h3310_42;

'd26 : lut_data <= '

h3324_07;

'd27 : lut_data <= '

h3325_07;

'd28 : lut_data <= '

h335b_ca;

'd29 : lut_data <= '

h335e_07;

'd30 : lut_data <= '

h335f_10;

'd31 : lut_data <= '

h3334_00;

'd32 : lut_data <= '

h3F01_04;

'd33 : lut_data <= '

h3F04_01;

'd34 : lut_data <= '

h3F05_30;

'd35 : lut_data <= '

h3626_01;

'd36 : lut_data <= '

h3635_60;

'd37 : lut_data <= '

h3631_84;

'd38 : lut_data <= '

h3636_8d;

//0607

'd39 : lut_data <= '

h3633_3f;

'd40 : lut_data <= '

h3639_80;

'd41 : lut_data <= '

h3622_1e;

'd42 : lut_data <= '

h3627_02;

'd43 : lut_data <= '

h3038_a4;

'd44 : lut_data <= '

h3621_18;

'd45 : lut_data <= '

h363a_1c;

'd46 : lut_data <= '

h3637_be;

'd47 : lut_data <= '

h3638_85;

'd48 : lut_data <= '

h363c_48;

// ramp cur

'd49 : lut_data <= '

h5780_ff;

// dpc

'd50 : lut_data <= '

h5781_04;

'd51 : lut_data <= '

h5785_10;

'd52 : lut_data <= '

h301e_e0;

// [4] 0:close tempsens

'd53 : lut_data <= '

h3662_82;

'd54 : lut_data <= '

h3d0d_00;

// close random code

'd55 : lut_data <= '

h3039_20;

'd56 : lut_data <= '

h303a_35;

//74.25M pclk

'd57 : lut_data <= '

h303b_00;

'd58 : lut_data <= '

h3306_46;

'd59 : lut_data <= '

h330b_a0;

'd60 : lut_data <= '

h3038_f8;

//pump clk div

'd61 : lut_data <= '

h320c_05;

//hts=3000

'd62 : lut_data <= '

h320d_dc;

'd63 : lut_data <= '

h320e_06;

//vts=1584

'd64 : lut_data <= '

h320f_30;

'd65 : lut_data <= '

h3202_00;

// ystart=48

'd66 : lut_data <= '

h3203_00;

'd67 : lut_data <= '

h3206_06;

// yend=1545 1545 rows selected

'd68 : lut_data <= '

h3207_08;

'd69 : lut_data <= '

h3200_01;

// xstart= 264

'd70 : lut_data <= '

h3201_08;

'd71 : lut_data <= '

h3204_09;

// xend = 2319 2056 cols selected

'd72 : lut_data <= '

h3205_0f;

'd73 : lut_data <= '

h3211_04;

// xstart

'd74 : lut_data <= '

h3213_04;

// ystart

'd75 : lut_data <= '

h3208_08;

//2048x1536

'd76 : lut_data <= '

h3209_00;

'd77 : lut_data <= '

h320a_06;

'd78 : lut_data <= '

h320b_00;

'd79 : lut_data <= '

h3312_06;

// sa1 timing

'd80 : lut_data <= '

h3340_04;

'd81 : lut_data <= '

h3341_d2;

'd82 : lut_data <= '

h3342_01;

'd83 : lut_data <= '

h3343_80;

'd84 : lut_data <= '

h335d_2a;

// cmp timing

'd85 : lut_data <= '

h3348_04;

'd86 : lut_data <= '

h3349_d2;

'd87 : lut_data <= '

h334a_01;

'd88 : lut_data <= '

h334b_80;

'd89 : lut_data <= '

h3368_03;

// auto precharge

'd90 : lut_data <= '

h3369_30;

'd91 : lut_data <= '

h336a_06;

'd92 : lut_data <= '

h336b_30;

'd93 : lut_data <= '

h3367_05;

'd94 : lut_data <= '

h330e_17;

'd95 : lut_data <= '

h3d08_00;

// pclk inv

'd96 : lut_data <= '

h303f_82;

'd97 : lut_data <= '

h3c03_28;

//fifo sram read position

'd98 : lut_data <= '

h3c00_45;

// Dig SRAM reset

'd99 : lut_data <= '

h3c03_02;

//anti smear

'd100 : lut_data <= '

h3211_06;

'd101 : lut_data <= '

h3213_06;

'd102 : lut_data <= '

h3620_82;

'd103 : lut_data <= '

h3630_b1;

//0x67

'd104 : lut_data <= '

h3635_60;

//0x66

'd105 : lut_data <= '

h3630_67;

'd106 : lut_data <= '

h3626_11;

'd107 : lut_data <= '

h363c_88;

//fine gain correction

'd108 : lut_data <= '

h3312_00;

'd109 : lut_data <= '

h3333_80;

'd110 : lut_data <= '

h3334_a0;

'd111 : lut_data <= '

h3620_62;

//0xd2

'd112 : lut_data <= '

h3300_10;

'd113 : lut_data <= '

h3627_06;

'd114 : lut_data <= '

h3312_06;

'd115 : lut_data <= '

h3340_03;

'd116 : lut_data <= '

h3341_80;

'd117 : lut_data <= '

h3334_20;

'd118 : lut_data <= '

h331e_10;

'd119 : lut_data <= '

h331f_13;

'd120 : lut_data <= '

h3320_18;

'd121 : lut_data <= '

h3321_18;

'd122 : lut_data <= '

h3039_30;

'd123 : lut_data <= '

h303a_2a;

//118.8M pclk

'd124 : lut_data <= '

h303b_00;

'd125 : lut_data <= '

h3640_02;

'd126 : lut_data <= '

h3641_01;

'd127 : lut_data <= '

h5000_21;

'd128 : lut_data <= '

h3340_04;

'd129 : lut_data <= '

h3342_02;

'd130 : lut_data <= '

h3343_60;

'd131 : lut_data <= '

h334a_02;

'd132 : lut_data <= '

h334b_60;

'd133 : lut_data <= '

h3306_66;

'd134 : lut_data <= '

h3367_01;

'd135 : lut_data <= '

h330b_ff;

'd136 : lut_data <= '

h3300_20;

'd137 : lut_data <= '

h331f_10;

'd138 : lut_data <= '

h3f05_e0;

'd139 : lut_data <= '

h3635_62;

'd140 : lut_data <= '

h3620_63;

//d2

'd141 : lut_data <= '

h3630_67;

//a9,

'd142 : lut_data <= '

h3633_3d;

'd143 : lut_data <= '

h3c00_00;

//[2]: 0 mipi->fifo

'd144 : lut_data <= '

h303f_02;

//[7]: 0 sel pll_pclk

'd145 : lut_data <= '

h3031_0a;

//[3:0] 10bit

'd146 : lut_data <= '

h3018_73;

//[7:5] sel lane=reg+1

'd147 : lut_data <= '

h3030_14;

'd148 : lut_data <= '

h3039_00;

'd149 : lut_data <= '

h303a_35;

'd150 : lut_data <= '

h303b_02;

'd151 : lut_data <= '

h303c_08;

'd152 : lut_data <= '

h3650_46;

'd153 : lut_data <= '

h3018_7a;

//close unused lane

'd154 : lut_data <= '

h3019_f0;

'd155 : lut_data <= '

h3010_e0;

//close dvp out

'd156 : lut_data <= '

h300f_ff;

'd157 : lut_data <= '

h300e_0f;

'd158 : lut_data <= '

h3640_00;

'd159 : lut_data <= '

h0100_01;

default

: lut_data <= 'h0000;

endcase

end

endmodule

|

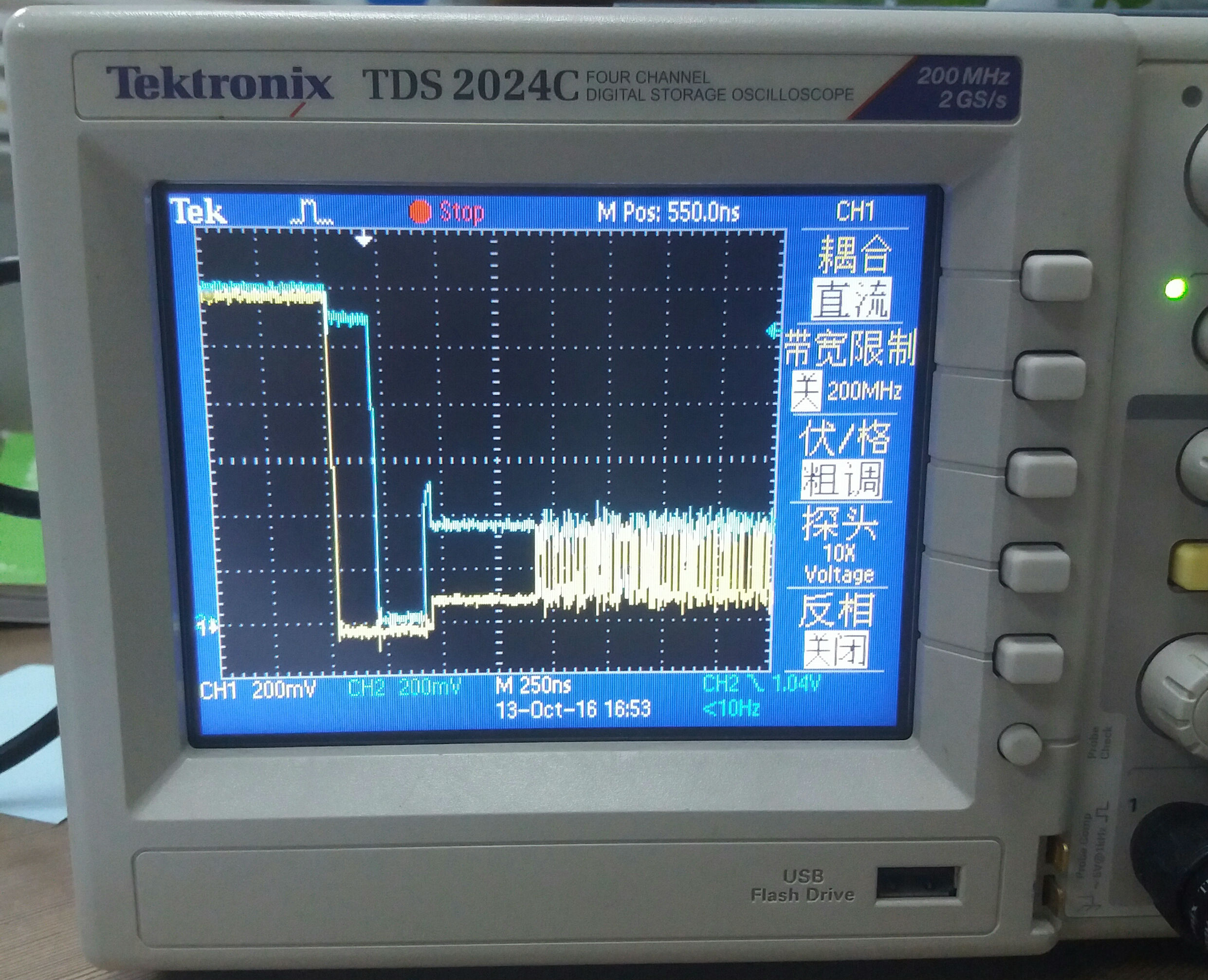

6.MIPI测试波形

用示波器两探头测得一路通道的差分波形,符合MIPI CSI电气规范。

7. 显示结果

HDMI正常显示,颜色显示正常。

本文转自 shugenyin 51CTO博客,原文链接:http://blog.51cto.com/shugenyin/1861393