1. 概述

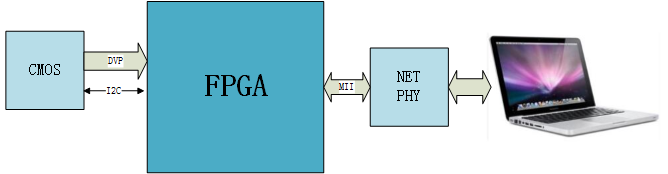

本设计采用FPGA技术,将CMOS摄像头(DVP接口)的视频数据采集,并通过以太网传输(UDP方式)给PC机,上位机DEMO通过套接字编程,将视频实时显示在屏幕上。

2. 硬件系统框图

CMOS采用OV7670(30万像素),FPGA采用ALTERA公司的CYCLONE IV,以太网卡采用REALTK公司的100M网卡芯片。

硬件平台采用ETree的FPGA开发板(某宝提供),如下图所示:

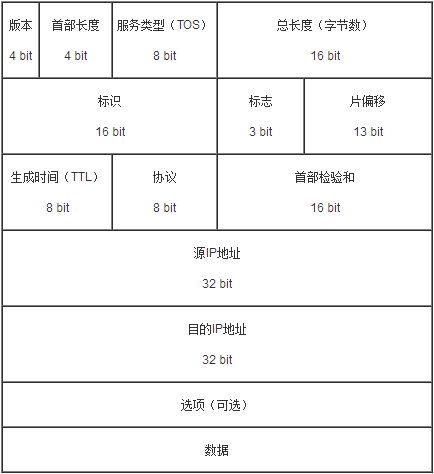

3. UDP/IP协议

UDP(User Datagram Protocol)是OSI参考模型中一种无连接的传输层协议,提供面向事务的简单不可靠信息传送服务。每一个数据包的前8个字节用来包含报头信息,剩余字节则用来包含具体的传输数据。UDP协议经常用于图像传输、网络监控数据交换等数据传输速度要求比较高的场合。

| UDP报文格式 |

|

| 0 15 |

16 31 |

| 源端口号 |

目的端口号 |

| 报文长度 |

校验和 |

| 数据 |

|

IP(Internet Protoco)包位于网络层,功能是把分组发往目标网络或主机。所有的TCP,UDP,IMCP,IGCP的数据都以IP数据格式传输。

以太网的数据帧的传输过程中,包长一般在46~1500字节,这里将UDP包长设计为:(8+20+640*2)=1308字节,以提高传输效率。

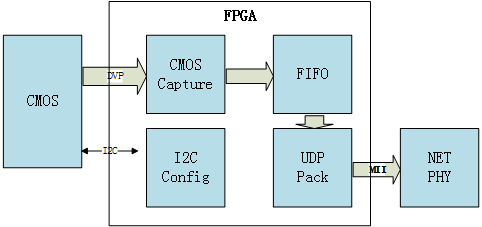

4. FPGA逻辑设计

FPGA各部分逻辑模块如下图所示:

-

CMOS Capture,采集CMOS的DVP视频流;

-

I2C Config,配置CMOS芯片;

-

FIFO,实现CMOS时钟域到以太网时钟域之间的转换;

-

UDP Pack,实现UDP/IP协议的实现。

下面为OV7670的初始化配置代码:

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

|

//file name: i2c_cfg_par.v

//creator: shugen.yin

//date: 2017-4-21

//function: i2c registers

//log: VGA RAW/25FPS, XCLK=24M

module i2c_cfg_par(

input [07:0] lut_index,

output reg [15:0] lut_data

);

always @(*)

begin

case

(lut_index)

//ov7670 RAW 25Fps 24M input

'd0 : lut_data <= '

h1280;

'd1 : lut_data <= '

h0000;

'd2 : lut_data <= '

h0000;

'd3 : lut_data <= '

h0000;

'd4 : lut_data <= '

h0000;

'd5 : lut_data <= '

h0000;

'd6 : lut_data <= '

h0000;

'd7 : lut_data <= '

h0000;

'd8 : lut_data <= '

h1101;

'd9 : lut_data <= '

h3a04;

'd10 : lut_data <= '

h1201;

//windows setting

'd11 : lut_data <= '

h1712;

//Hstart high 8bit

'd12 : lut_data <= '

h1800;

//Hstop high 8bit

'd13 : lut_data <= '

h1902;

//Vstart high 8bit

'd14 : lut_data <= '

h1a7a;

//Vstop high 8bit

'd15 : lut_data <= '

h32b6;

//HREF

'd16 : lut_data <= '

h0300;

//VREF

'd17 : lut_data <= '

h0c00;

'd18 : lut_data <= '

h3e00;

'd19 : lut_data <= '

h703a;

'd20 : lut_data <= '

h7135;

'd21 : lut_data <= '

h7211;

'd22 : lut_data <= '

h73f0;

'd23 : lut_data <= '

ha202;

'd24 : lut_data <= '

h13e0;

'd25 : lut_data <= '

h0000;

'd26 : lut_data <= '

h0d40;

'd27 : lut_data <= '

h1438;

'd28 : lut_data <= '

ha507;

'd29 : lut_data <= '

hab08;

'd30 : lut_data <= '

h2495;

'd31 : lut_data <= '

h2533;

'd32 : lut_data <= '

h26e3;

'd33 : lut_data <= '

h9f78;

'd34 : lut_data <= '

ha068;

'd35 : lut_data <= '

ha10b;

'd36 : lut_data <= '

ha6d8;

'd37 : lut_data <= '

ha7d8;

'd38 : lut_data <= '

ha8f0;

'd39 : lut_data <= '

ha990;

'd40 : lut_data <= '

haa94;

'd41 : lut_data <= '

h13e5;

'd42 : lut_data <= '

h0e61;

'd43 : lut_data <= '

h0f4b;

'd44 : lut_data <= '

h1602;

'd45 : lut_data <= '

h2102;

'd46 : lut_data <= '

h2291;

'd47 : lut_data <= '

h2907;

'd48 : lut_data <= '

h3303;

'd49 : lut_data <= '

h350b;

'd50 : lut_data <= '

h371c;

'd51 : lut_data <= '

h3871;

'd52 : lut_data <= '

h3c78;

'd53 : lut_data <= '

h3d08;

'd54 : lut_data <= '

h413a;

'd55 : lut_data <= '

h4d40;

'd56 : lut_data <= '

h4e20;

'd57 : lut_data <= '

h6955;

'd58 : lut_data <= '

h6b4a;

'd59 : lut_data <= '

h7419;

'd60 : lut_data <= '

h7661;

'd61 : lut_data <= '

h8d4f;

'd62 : lut_data <= '

h8e00;

'd63 : lut_data <= '

h8f00;

'd64 : lut_data <= '

h9000;

'd65 : lut_data <= '

h9100;

'd66 : lut_data <= '

h9600;

'd67 : lut_data <= '

h9a80;

'd68 : lut_data <= '

hb08c;

'd69 : lut_data <= '

hb10c;

'd70 : lut_data <= '

hb20e;

'd71 : lut_data <= '

hb382;

'd72 : lut_data <= '

hb80a;

'd73 : lut_data <= '

h4314;

'd74 : lut_data <= '

h44f0;

'd75 : lut_data <= '

h4534;

'd76 : lut_data <= '

h4658;

'd77 : lut_data <= '

h4728;

'd78 : lut_data <= '

h483a;

'd79 : lut_data <= '

h5988;

'd80 : lut_data <= '

h5a88;

'd81 : lut_data <= '

h5b44;

'd82 : lut_data <= '

h5c67;

'd83 : lut_data <= '

h5d49;

'd84 : lut_data <= '

h5e0e;

'd85 : lut_data <= '

h6c0a;

'd86 : lut_data <= '

h6d55;

'd87 : lut_data <= '

h6e11;

'd88 : lut_data <= '

h6f9f;

'd89 : lut_data <= '

h6a40;

'd90 : lut_data <= '

h0140;

'd91 : lut_data <= '

h0240;

'd92 : lut_data <= '

h13e7;

'd93 : lut_data <= '

h3411;

'd94 : lut_data <= '

h9266;

'd95 : lut_data <= '

h3b0a;

'd96 : lut_data <= '

ha488;

'd97 : lut_data <= '

h9600;

'd98 : lut_data <= '

h9730;

'd99 : lut_data <= '

h9820;

'd100 : lut_data <= '

h9920;

'd101 : lut_data <= '

h9a84;

'd102 : lut_data <= '

h9b29;

'd103 : lut_data <= '

h9c03;

'd104 : lut_data <= '

h9d4c;

'd105 : lut_data <= '

h9e3f;

'd106 : lut_data <= '

h7804;

'd107 : lut_data <= '

h7901;

'd108 : lut_data <= '

hc8f0;

'd109 : lut_data <= '

h790f;

'd110 : lut_data <= '

hc820;

'd111 : lut_data <= '

h7910;

'd112 : lut_data <= '

hc87e;

'd113 : lut_data <= '

h790b;

'd114 : lut_data <= '

hc801;

'd115 : lut_data <= '

h790c;

'd116 : lut_data <= '

hc807;

'd117 : lut_data <= '

h790d;

'd118 : lut_data <= '

hc820;

'd119 : lut_data <= '

h7902;

'd120 : lut_data <= '

hc8c0;

'd121 : lut_data <= '

h7903;

'd122 : lut_data <= '

hc840;

'd123 : lut_data <= '

h7905;

'd124 : lut_data <= '

hc830;

'd125 : lut_data <= '

h7926;

default

: lut_data <= 'h0000;

endcase

end

endmodule

|

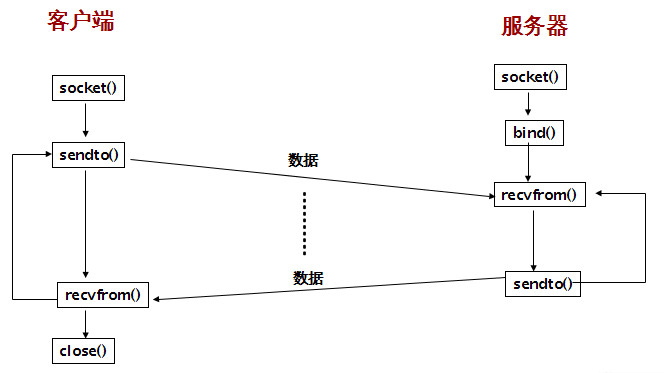

5. 上位机Demo实现

本设计采用VC++ 2010设计了一款简易的UDP网络视频流播放器,视频源为RAW8格式,分辨率640*480,帧率25Hz。Windows为我们提供了便捷的套接字(socket)编程方式,软件工程师方便实现网络编程。

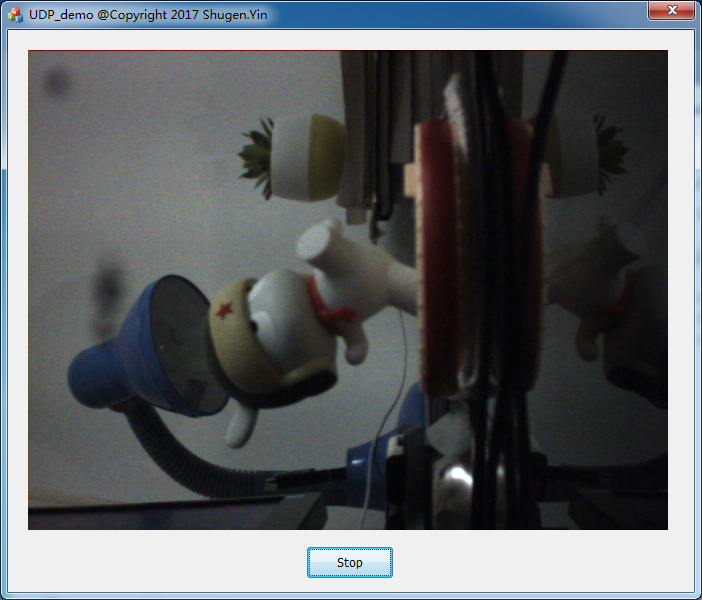

6. 视频显示结果

给FPGA板卡上电,打开UDP demo软件,视频正常显示。

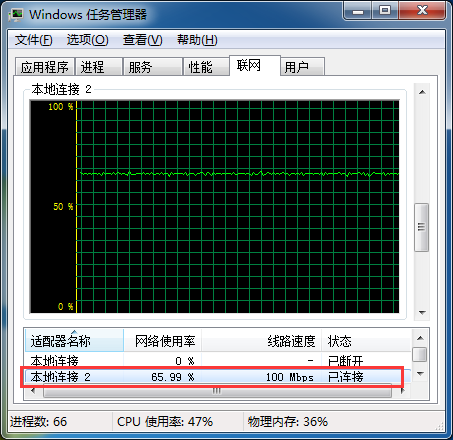

7. 任务管理器

在任务管理器中,可以查看网卡的状态,包括使用率和丢包的大概曲线图。UDP demo软件运行几分钟后,图像稳定显示,从任务管理器中可以看到本地网卡2的使用率为65.99%,曲线平整,没有异常丢包情况。

本文转自 shugenyin 51CTO博客,原文链接:http://blog.51cto.com/shugenyin/1918406