1. 概述

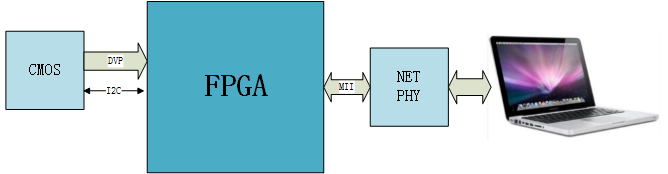

本设计采用FPGA技术,将CMOS摄像头(DVP接口)的视频数据采集,并通过以太网传输(UDP方式)给PC机,上位机DEMO通过套接字编程,将视频实时显示在屏幕上。

2. 硬件系统框图

CMOS采用MT9V011(30万像素),FPGA采用ALTERA公司的CYCLONE IV,以太网卡采用REALTK公司的100M网卡芯片,硬件框图如下:

硬件平台采用ETree的FPGA开发板(某宝提供),如下图所示:

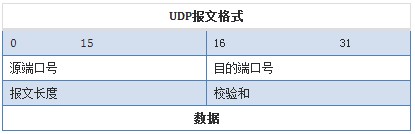

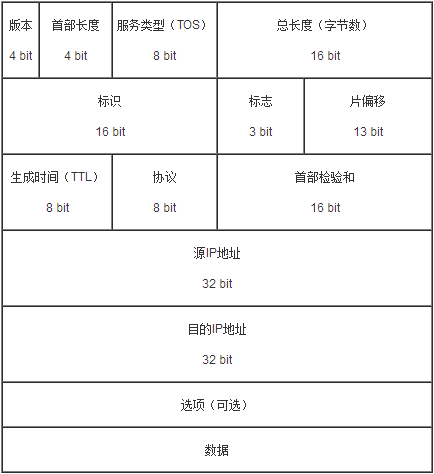

3. UDP/IP协议

UDP(User Datagram Protocol)是OSI参考模型中一种无连接的传输层协议,提供面向事务的简单不可靠信息传送服务。每一个数据包的前8个字节用来包含报头信息,剩余字节则用来包含具体的传输数据。UDP协议经常用于图像传输、网络监控数据交换等数据传输速度要求比较高的场合。

IP(Internet Protoco)包位于网络层,功能是把分组发往目标网络或主机。所有的TCP,UDP,IMCP,IGCP的数据都以IP数据格式传输。

以太网的数据帧的传输过程中,包长一般在46~1500字节,这里将UDP包长设计为:(8+20+640*2)=1308字节,以提高传输效率。

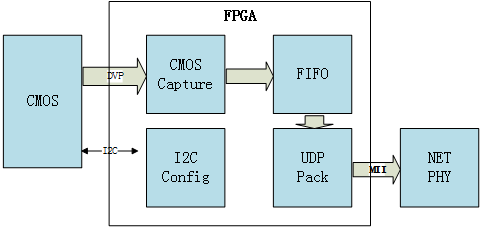

4. FPGA逻辑设计

FPGA各部分逻辑模块如下图所示:

-

CMOS Capture,采集CMOS的DVP视频流;

-

I2C Config,配置CMOS芯片;

-

FIFO,实现CMOS时钟域到以太网时钟域之间的转换;

-

UDP Pack,实现UDP/IP协议的实现。

下面为MT9V011的初始化配置代码:

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

|

reg [23:0]lut_data;

reg [7:0]lut_index;

always @(*)

begin

case

(lut_index)

0 : lut_data <= 24'h01_000b;

//First row to read

1 : lut_data <= 24'h02_0012;

//Firts column to read

2 : lut_data <= 24'h05_0083;

//bit 0-9 h-blank

3 : lut_data <= 24'h06_001c;

//bit 0-11 v-blank

4 : lut_data <= 24'h35_0313;

//global gain: 0-6(initial gain) 7-8(analog gain) 9-10(total gain)

5 : lut_data <= 24'h20_1000;

//bit 15: upside down, bit 14: mirror(right to left)

// 6 : lut_data <= 24'h07_3302; //bit 2: chip enable, bit 15: pclk invert, 8-11

7 : lut_data <= 24'h09_01cf;

//bit 0-11, shutter width

default

:lut_data <= 24'h000000;

endcase

end

|

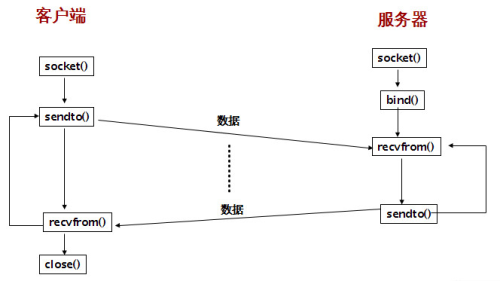

5. 上位机Demo实现

本设计采用VC++ 2010设计了一款简易的UDP网络视频流播放器,视频源为RAW8格式,分辨率640*480,帧率25Hz。Windows为我们提供了便捷的套接字(socket)编程方式,软件工程师方便实现网络编程。

6. 视频显示结果

给FPGA板卡上电,打开UDP demo软件,视频正常显示,效果比OV7670好很多,如下图所示。

本文转自 shugenyin 51CTO博客,原文链接:http://blog.51cto.com/shugenyin/1970271