1. 概述

本设计采用FPGA技术,实现CMOS视频图像的中值滤波,并通过以太网传输(UDP方式)给PC实时显示。

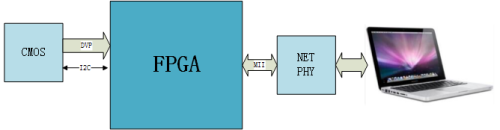

2. 硬件系统框图

CMOS采用MT9V011(30万像素),FPGA采用ALTERA公司的CYCLONE IV,以太网卡采用REALTK公司的100M网卡芯片,硬件框图如下:

硬件平台采用ETree的FPGA开发板,如下图所示:

3. 算法原理

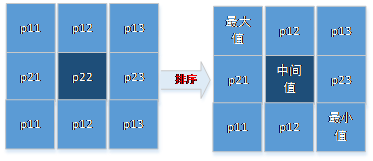

中值滤波需要对3×3矩阵窗里的像素进行排序,然后找到中间值替换原始像素。

中值滤波对消除椒盐噪声非常有效,在图像处理中常用于保护边缘信息。

4. 算法实现

实现中值滤波关键是实现3×3矩阵窗内的实时排序,这里可以使用全比较法,为窗内的每个像素定义一个计数器cntn(n=0,1,2,3,4,5,6,7)来记录比较结果,最后cntn为4的值便是中间值,将对应的像素替换成原始像素即可。

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

|

always @(*)

if

(cmos_vsync)

cnt0 <= 0;

else

cnt0 <= (taps0x>taps0x) + (taps0x_r0>taps0x) + (taps0x_r1>taps0x) +

(taps1x>taps0x) + (taps1x_r0>taps0x) + (taps1x_r1>taps0x) +

(taps2x>taps0x) + (taps2x_r0>taps0x) + (taps2x_r1>taps0x);

... ...

always @(posedge cmos_pclk)

if

(cmos_vsync)

begin

cmos_href_o <= 0;

cmos_vsync_o <= 0;

cmos_data_o <= 0;

end

else

begin

cmos_href_o <= cmos_href_r1;

cmos_vsync_o <= cmos_vsync;

cmos_data_r0 <= (cnt0==4)?taps0x:

(cnt1==4)?taps0x_r0:

(cnt2==4)?taps0x_r1:

(cnt3==4)?taps1x:

(cnt4==4)?taps1x_r0:

(cnt5==4)?taps1x_r1:

(cnt6==4)?taps2x:

(cnt7==4)?taps2x_r0:

(cnt8==4)?taps2x_r1:8'h01;

cmos_data_o <= cmos_data_r0;

end

|

5. 最终效果

下图为原始图片效果。

中值滤波后的效果图如下,图像中的数字变骨感一些。

本文转自 shugenyin 51CTO博客,原文链接:http://blog.51cto.com/shugenyin/1976972