直达最佳实践:【FPGA加速广告CTR预估】

最佳实践频道:【点击查看更多上云最佳实践】

这里有丰富的企业上云最佳实践,从典型场景入门,提供一系列项目实践方案,降低企业上云门槛的同时满足您的需求!

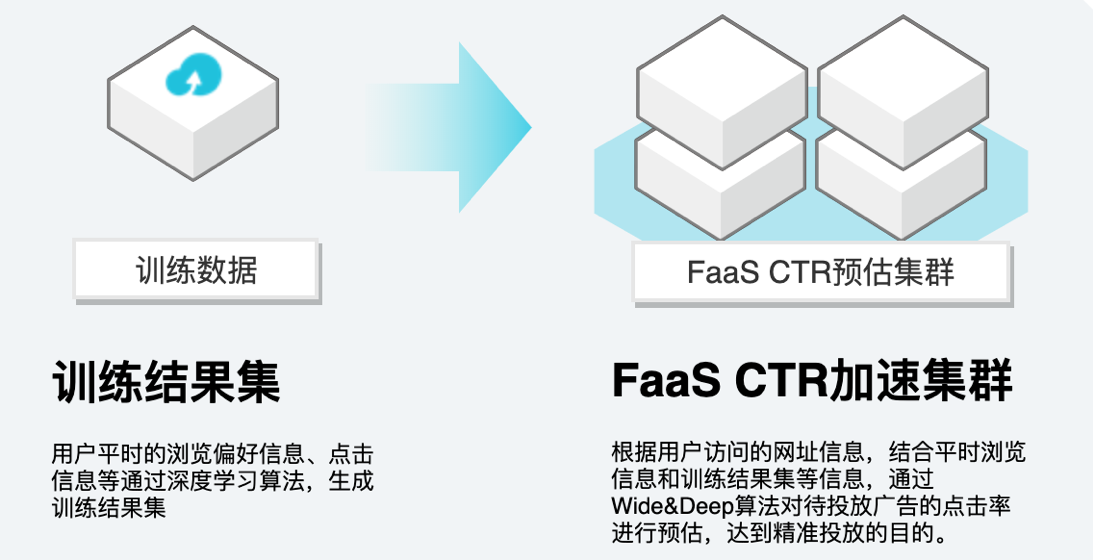

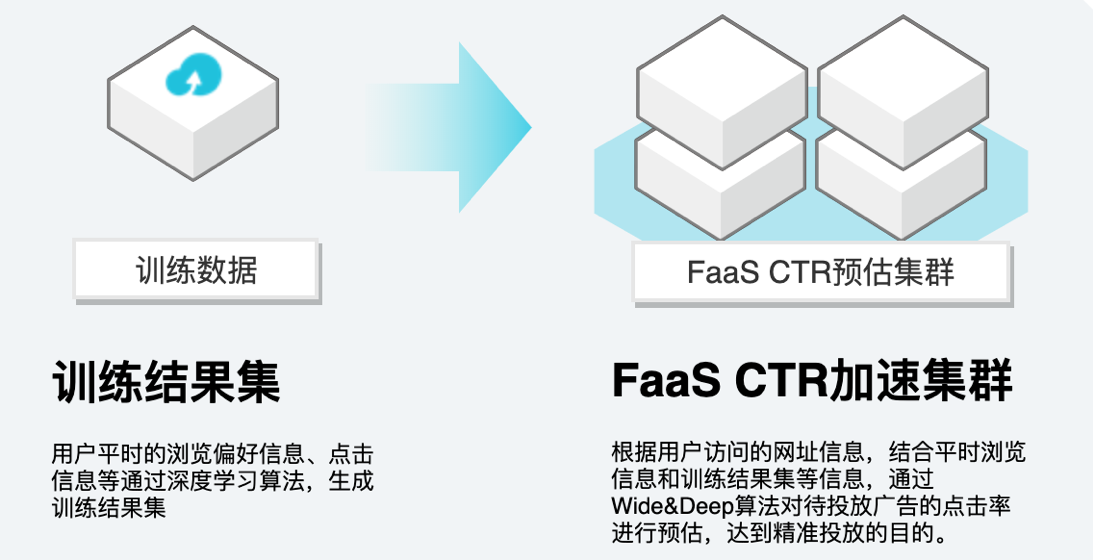

场景描述

基于阿里云FPGA计算型实例,完整演示加速广告CTR预估的场景,帮助使用者快速理解阿里云FPGA云服务器。

解决问题

使用FPGA云服务器加速CTR(广告点击率)预估

产品列表

- 专有网络VPC

- 弹性计算ECS

- FPGA云服务器

直达最佳实践:【FPGA加速广告CTR预估】

最佳实践频道:【点击查看更多上云最佳实践】

这里有丰富的企业上云最佳实践,从典型场景入门,提供一系列项目实践方案,降低企业上云门槛的同时满足您的需求!

基于阿里云FPGA计算型实例,完整演示加速广告CTR预估的场景,帮助使用者快速理解阿里云FPGA云服务器。

使用FPGA云服务器加速CTR(广告点击率)预估